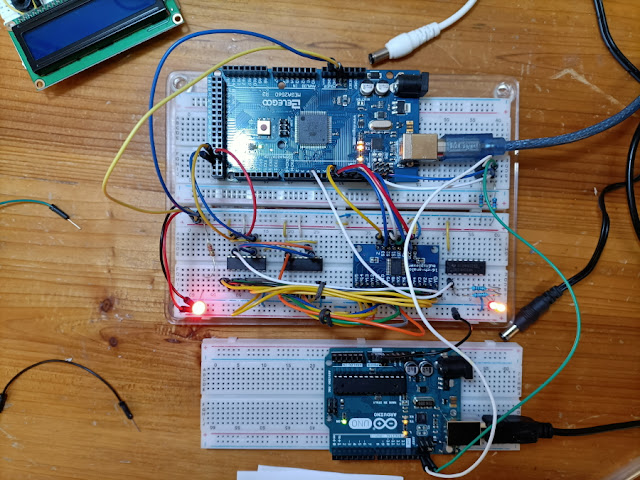

This post is the follow up, and the counterpart, of the previous one (112-bit T stream To 5N1 frames, just read it for background). If while receiving we need a "downsampling" by a factor of 16 of the 112-bit period stream coming from the modem, when transmitting we have to expand the source 5N1 frames bitwise by the same factor before to forward them to the modem. As in the "downsampler", I used the multiplexer/demultiplexer module CD74HC4067 and two I2C connected Arduino boards.

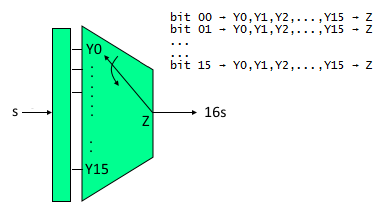

Each bit of the 5N1 frames is spread to a 16-bit D-type latch register which is three-state connected to the 16-input of the multiplexer, the inputs are then selected and forwarded to the multiplexer serial output at a speed that is 16 times faster than the 5N1 frames (figs. 1,2).

| |

| Fig.1 |

|

| Fig. 2 |

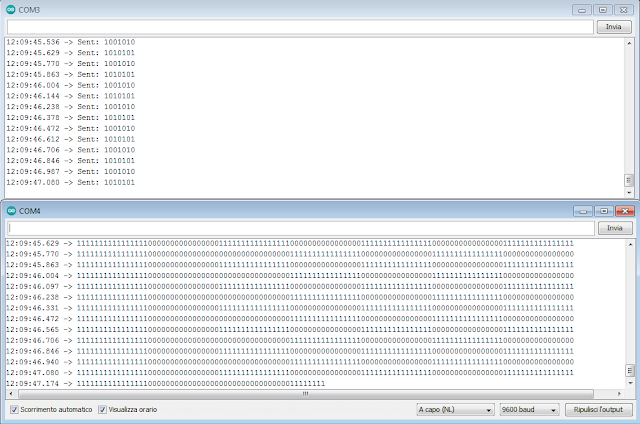

The 5N1-112 conversion is not done via software: a board takes care of sending data to the other one which forwards 'em and manages the ICs. Input/output data are dispalyed on the serial ports (COM3 on the sender, COM4 on the receive expander, see figure 3 below).

|

| Fig. 3 |

As already mentioned in the cited post, I do not aim to "replicate" the circuit used to perform the 5N1-112 conversion but only try to simulate its operation through the use of a multiplexer. For those interested in playing with the two circuits (...but I really don't think so) the 4 rough "sketches" can be downloaded from here along with the data sheets of the used ICs:

https://disk.yandex.com/d/SVTcXiikai1VRQ

No comments:

Post a Comment